Ace Tips About Why Is Verilog Not VHDL

Decoding the Digital Dilemma

1. Choosing Your Hardware Description Language

Ever wondered why some engineers swear by Verilog while others champion VHDL? It's not just a matter of personal preference, though that certainly plays a role! The world of hardware description languages (HDLs) can seem like alphabet soup, but understanding the nuances between Verilog and VHDL can significantly impact your digital design projects. Both are powerful tools used to describe and simulate digital circuits, but they have distinct characteristics that make them better suited for different tasks and different design philosophies. Think of it like choosing between a sturdy pickup truck (Verilog) and a meticulously crafted sports car (VHDL) — both get you where you need to go, but the experience is vastly different.

One key difference lies in their origins and design philosophy. Verilog, born in the 1980s, has roots in gate-level modeling and simulation. This means it's historically been closer to the hardware itself, making it easier to visualize how the code translates into actual circuits. VHDL, on the other hand, emerged from a U.S. Department of Defense initiative aiming for a more standardized and formal approach. This focus on standardization and rigorous specification makes VHDL particularly attractive for complex, safety-critical applications, like aerospace or medical devices.

Think of it this way: Verilog is like sketching your idea on a napkin — quick and easy to get started. VHDL is more like creating detailed blueprints before building anything. Both are useful, but they cater to different approaches and levels of formality. Choosing between them depends heavily on the project's requirements, team expertise, and the tools available.

The choice isn't always straightforward, and it often comes down to balancing ease of use, level of control, and the need for rigorous documentation. Many engineers today are proficient in both languages, allowing them to select the best tool for each specific job. So, let's dive deeper into some of the factors that sway the decision.

Syntax and Structure

2. Comparing Code Styles

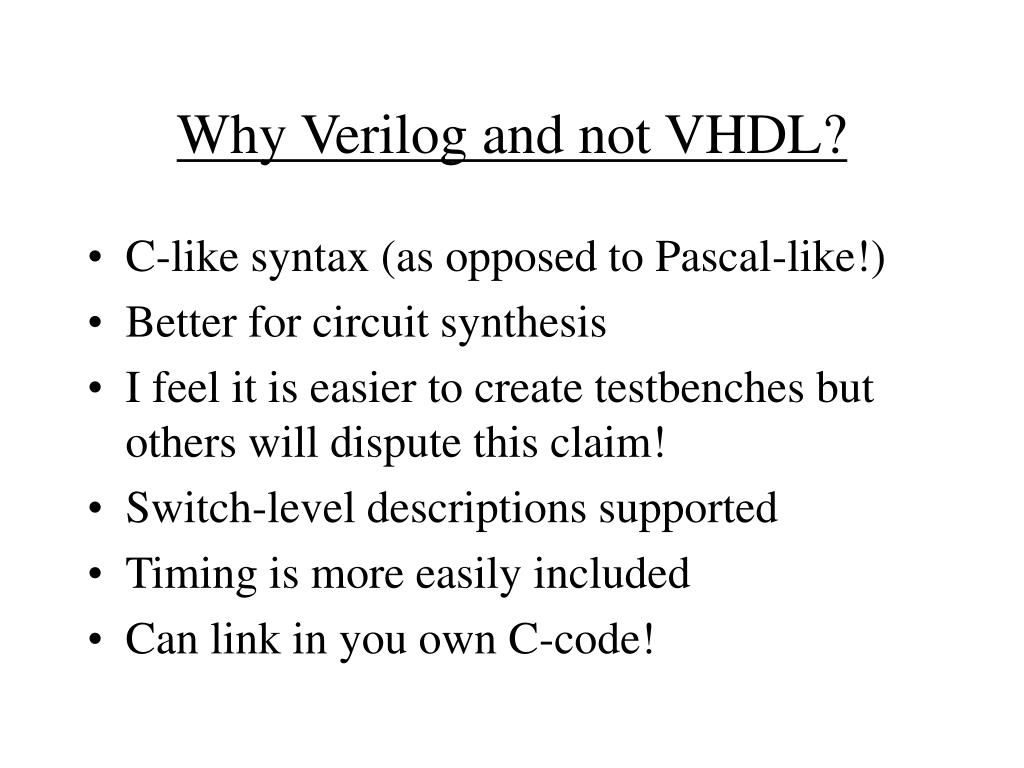

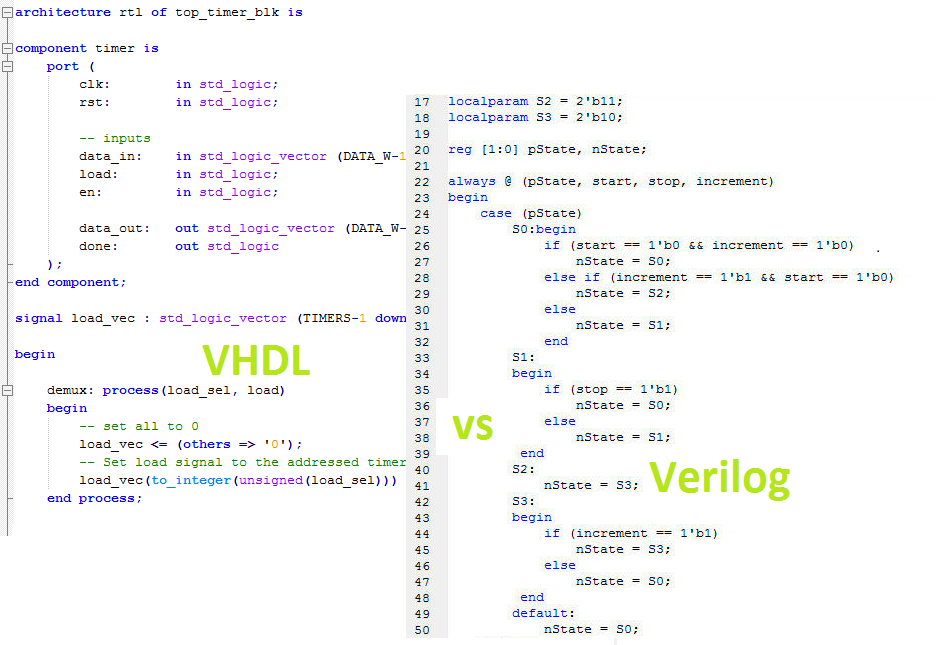

Verilog and VHDL differ significantly in their syntax. Verilog is often described as being more "C-like," making it easier for software engineers to pick up. Its syntax is relatively concise and forgiving, allowing for rapid prototyping and experimentation. However, this flexibility can also lead to less structured code if not carefully managed. Imagine Verilog as a casual conversation — you can express yourself freely, but you might occasionally stumble over your words.

VHDL, in contrast, has a more verbose and strictly typed syntax. This means you need to be precise about declaring variables, specifying data types, and defining signals. While this can initially seem more cumbersome, it promotes better code readability and reduces the chances of subtle errors slipping through. Think of VHDL as writing a formal legal document — every detail is meticulously defined to avoid ambiguity.

This difference in syntax has implications for the learning curve. Verilog generally has a shallower learning curve, making it easier for beginners to get started. VHDL, with its stricter rules and more complex constructs, requires a more significant initial investment in learning. However, the payoff is often higher in terms of code maintainability and reliability, especially for large and complex projects. The upside of VHDL's strictness is the compiler catches most errors during compilation, saving tons of debug time later.

Consider this simple example: if you're quickly prototyping a simple circuit, Verilog's ease of use might be preferable. But if you're developing a complex, safety-critical system that needs to be thoroughly verified, VHDL's rigor and formality might be the better choice.

PPT Introduction To HDLs PowerPoint Presentation, Free Download ID

Industry Adoption and Tool Support

3. Understanding Market Trends

The landscape of industry adoption and tool support for Verilog and VHDL is constantly evolving. Historically, Verilog has been more prevalent in the semiconductor industry, particularly in North America and Asia. VHDL, on the other hand, has been widely adopted in Europe and in industries with a strong emphasis on formal verification, such as aerospace and defense.

However, the lines are blurring as both languages have become increasingly popular worldwide. Many companies now use both Verilog and VHDL depending on the specific project requirements and the expertise of their engineering teams. The availability of robust tool support is another crucial factor. All major EDA (Electronic Design Automation) vendors offer comprehensive support for both languages, including simulators, synthesis tools, and formal verification tools.

The open-source community also plays a significant role. There are several open-source simulators and synthesis tools available for both Verilog and VHDL, making them accessible to hobbyists, students, and small companies with limited budgets. The continued growth of open-source tools is helping to democratize hardware design and foster innovation. Companies like Xilinx and Intel (Altera) invest heavily in supporting both.

Ultimately, the choice of language often depends on the specific industry, the company's culture, and the availability of skilled engineers. Some companies have standardized on one language to streamline their workflow and reduce training costs, while others allow their engineers to choose the best tool for each individual project.

Images Of Verilog JapaneseClass.jp

Expressiveness and Abstraction

4. Exploring Design Capabilities

Both Verilog and VHDL offer different levels of expressiveness and abstraction. Verilog, with its roots in gate-level modeling, allows engineers to describe circuits at a very low level of detail. This is useful for fine-tuning performance and optimizing area, but it can also be tedious and time-consuming for complex designs. It's like building a house brick by brick — you have complete control, but it takes a lot of effort.

VHDL, with its strong support for data types and abstract data structures, allows engineers to describe circuits at a higher level of abstraction. This enables them to focus on the overall functionality of the design without getting bogged down in the details of the underlying hardware. This is like designing the layout of the house and letting the builders handle the bricklaying — you focus on the big picture, and the details are taken care of automatically.

Modern versions of both languages have incorporated features that allow for higher levels of abstraction, such as behavioral modeling and transaction-level modeling. These features enable engineers to describe circuits in terms of their behavior rather than their structure, making it easier to design and verify complex systems. You can even implement sophisticated algorithms and mathematical functions in both!

The level of abstraction required depends on the complexity of the design and the goals of the project. For simple designs, a lower level of abstraction might be sufficient. But for complex systems, a higher level of abstraction is often necessary to manage the complexity and reduce development time. Therefore, it's not necessarily about one language is better than the other, it really boils down to use the right language in the right situation.

![Unerring Language VHDL Vs VERILOG [2023] Unerring Language VHDL Vs VERILOG [2023]](https://www.logic-fruit.com/wp-content/uploads/2021/09/VHDL-VS-VERILOG-Thumbnail-1024x538.jpg)

Debugging and Verification

5. Ensuring Code Quality

Debugging and verification are critical aspects of hardware design. Both Verilog and VHDL offer various mechanisms for simulating and verifying designs, but they differ in their approaches. Verilog's more relaxed syntax can sometimes make it harder to catch subtle errors during compilation, requiring more extensive simulation to uncover bugs. It's like trying to find a needle in a haystack — the haystack is smaller, but the needle is harder to spot.

VHDL's stricter syntax, on the other hand, helps to catch many errors during compilation, reducing the need for extensive simulation. This can save significant time and effort, especially for large and complex designs. It's like having a metal detector that helps you quickly find the needle — the haystack might be bigger, but the needle is easier to locate.

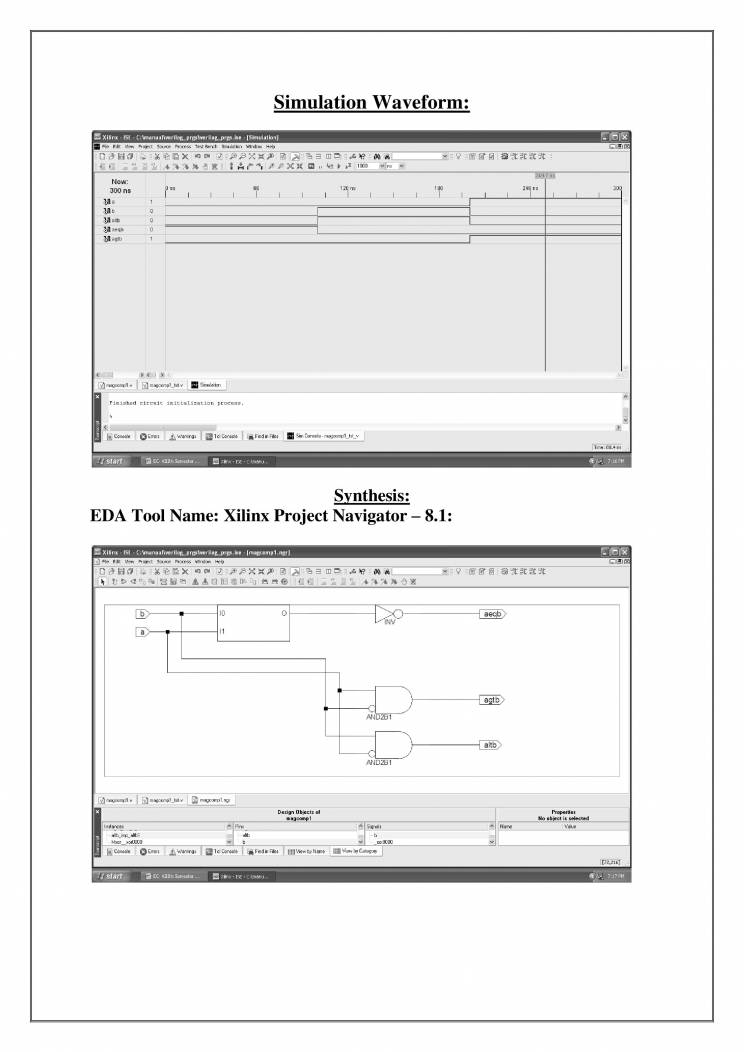

Both languages support various verification techniques, including simulation, formal verification, and hardware emulation. Simulation involves running the design through a series of test cases to verify its functionality. Formal verification uses mathematical techniques to prove that the design meets its specifications. Hardware emulation involves running the design on a specialized hardware platform that mimics the behavior of the target hardware. The correct implementation and debug stage is often the most time consuming step in a hardware project.

The choice of verification technique depends on the complexity of the design and the level of confidence required. For critical applications, formal verification is often used to ensure that the design is free of errors. For less critical applications, simulation might be sufficient. Therefore, the debug and verification phase is an essential part of the whole hardware design process.

FAQ

Q: Is Verilog easier to learn than VHDL?A: Generally, yes. Verilog's syntax is more similar to C, making it easier for programmers to pick up. However, VHDL's strictness can help catch errors earlier in the design process.

Q: Which language is better for beginners?A: Verilog is often recommended for beginners due to its simpler syntax. But don't let that discourage you from learning VHDL if your projects demand it!

Q: Are Verilog and VHDL compatible?A: Not directly, but you can often integrate designs written in both languages using mixed-language simulation tools. So, you're not necessarily locked into one language forever!

Q: Which language should I learn if I want to work in the semiconductor industry?A: While both are used, Verilog is often more prevalent in the semiconductor industry, especially in North America and Asia. However, knowing both languages is a valuable asset.